# Four Sample Applications for the KS57-Series Basic Timer Module

**Application Note: KS57APN1**

Application Engineering Department LSI 2 Division, Micom Sector

# **BASIC TIMER APPLICATIONS**

#### USING THE BASIC TIMER AS AN INTERVAL TIMER

The primary function of the basic timer (BT) is to measure elapsed time intervals. You can program the KS57series basic timer module to measure four different time intervals, based on the selected CPU clock. The basic timer module includes a BT mode register, BMOD, and an 8-bit counter, BCNT.

The BCNT value is incremented each time a clock signal is detected which corresponds to the frequency you select using BMOD register settings. When a counter overflow occurs, the basic timer interrupt request flag, IRQB (location FB8H.0), is set to "1" to signal that the designated time interval has elapsed. Next, the basic timer interrupt is generated, BCNT is cleared to zero, and counting resumes from 00H.

You can restart the basic timer (and clear the BCNT value) at any time by setting BMOD.3 to "1".

#### Setting the Basic Timer Interval

The following program example shows how to set the basic timer interval:

| BITS | EMB      |   |                                                  |

|------|----------|---|--------------------------------------------------|

| SMB  | 15       |   |                                                  |

| LD   | A,#1011B |   |                                                  |

| LD   | BMOD,A   | ; | Set the IRQB flag every 31.3 ms (fxx = 4.19 MHz) |

#### **Reading the BCNT Value**

To eliminate the possibility of reading unstable data while the counter is incrementing, always execute a BCNT read operation twice. If, after two consecutive read operations, the BCNT values match, you can select the latter value as valid data. Continue to read the BCNT value, however, until this validation condition is met.

The following program code illustrates the looping read operation for BCNT:

|      | BITS<br>SMB<br>LD | EMB<br>15<br>HL,#BCNT   |               |

|------|-------------------|-------------------------|---------------|

| LOOP |                   |                         |               |

|      | LD<br>LD          | EA,@HL<br>YZ,EA         | ; First read  |

|      | LD<br>CPSE<br>JR  | EA,@HL<br>EA,YZ<br>LOOP | ; Second read |

#### USING THE BASIC TIMER AS A WATCHDOG TIMER

You can use the basic timer as a watchdog timer to prevent program overruns or to escape from an infinite loop. To implement this function in an application program, follow these guidelines:

- 1. Divide a program into several modules and estimate the time it takes the MCU to process each module under normal operating conditions.

- 2. Set the basic timer interval for each module to be longer than the module's normal processing time. This basic timer interval setting should be performed at the start of each program module.

- 3. When the pre-set basic timer interval of a program module has elapsed, the BT counter (BCNT) should be reset and the BT restarted.

- 4. If the BT cannot be restarted within the program module's normal execution time, a basic timer interrupt is generated to signal a possible system malfunction.

#### Source Code for Watchdog Timer Routine

:===

| ;======      | =======                                    |                                        |                                                                                               |

|--------------|--------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------|

| ; Reset rou  | tine:                                      |                                        |                                                                                               |

| RESET        | •                                          |                                        |                                                                                               |

|              | •<br>BITS<br>SMB<br>LD<br>LD<br>BITS<br>EI | EMB<br>15<br>A,#1101B<br>BMOD,A<br>IEB | ; Make BT settings and start                                                                  |

| ;======      |                                            |                                        |                                                                                               |

| ; Main routi | ne:                                        |                                        |                                                                                               |

| MAIN         | CALL<br>CALL<br>JP                         | MODULE1<br>MODULE2<br>MAIN             | ; After 31.3 ms (BMOD = #0BH, fxx = 4.19 MHz)<br>; After 7.8 ms (BMOD = #0DH, fxx = 4.19 MHz) |

| MODULE1      | BITS<br>SMB<br>LD<br>LD<br>•<br>•          | EMB<br>15<br>A,#1011B<br>BMOD,A        |                                                                                               |

|              | BITS<br>SMB<br>BITS                        | EMB<br>15<br>BMOD.3                    |                                                                                               |

RET Source Code for Watchdog Timer Routine (Cont.) MODULE2

| BITS<br>SMB<br>LD<br>LD<br>•    | EMB<br>15<br>A,#1011B<br>BMOD,A |

|---------------------------------|---------------------------------|

| •<br>BITS<br>SMB<br>BITS<br>RET | EMB<br>15<br>BMOD.3             |

| BITR<br>BITR<br>JP              | IS0<br>IS1<br>RESET             |

#### USING THE BASIC TIMER TO RECEIVE SIGNALS FROM A REMOTE CONTROLLER

#### **Function Description**

INTB

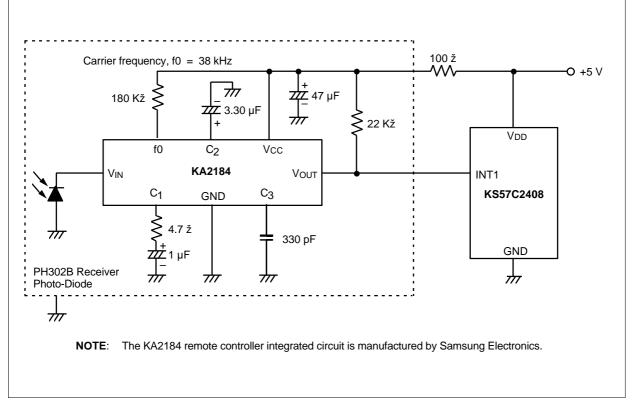

The application program described in this section uses the basic timer to receive data transmitted from a remote controller. The remote controller signal is input at the INT1 pin of a KS57-series microcontroller through a preamplifier circuit, as shown in Figure 1-1.

To encode the data, the time intervals between remote control signals are measured. A typical remote controller signal consists of a leader pulse, custom code, and data code (see KS57APN10). A remote controller receiver circuit inverts the received signal and removes the carrier frequency.

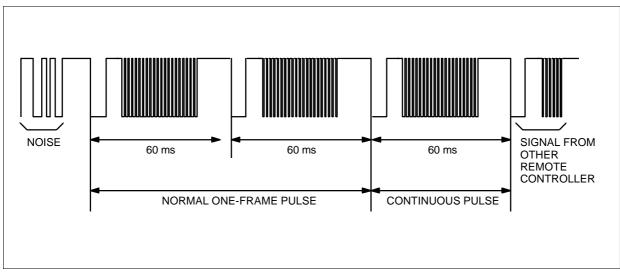

In an actual application, considerable circuit noise may occur before the leader code is received. To protect against signal disruption by this noise, this sample program uses the basic timer to detect the falling edge of the leader code at the external interrupt input pin (INT1).

Figure 1-1. Remote Controller Carrier Signal (f0) Receiver Circuit

Figure 1-2. Waveform Received From Remote Controller

#### **RAM Allocation**

Γ

| Address                  | 40H   | 41H                                    | 42H                                                                         | 43H                                                | 44H                                             | 45H | 46H | 47H | 48H | 49H | 4AH | 4BH | 4CH | 4DH | 4EH |

|--------------------------|-------|----------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Data Value<br>(see NOTE) | 1     | 1                                      | 2                                                                           | 3                                                  |                                                 |     | 4   |     |     | 5   |     | 6   |     | 7   | 8   |

|                          | NOTE: | 2 =<br>3 =<br>4 =<br>5 =<br>6 =<br>7 = | STATE<br>LECN<br>REDA<br>Not us<br>CODE<br>VALID<br>Flags:<br>VALFC<br>CPFG | E (1 nibl<br>F (1 nibl<br>TA (5 ni<br>ed<br>BUF (2 | ole)<br>ole)<br>bbles)<br>nibbles<br>les)<br>0) | i)  |     |     |     |     |     |     |     |     |     |

#### Figure 1-3. RAM Allocation for Basic Timer Remocon Application

For this application, data RAM is allocated to addresses 40H–4EH of memory bank 0, where

| CPCNT:         | Counts the elapsed time since a valid code was input            |

|----------------|-----------------------------------------------------------------|

| STATE:         | Mode status, indicating the last signal edge which was detected |

| LECNT:         | Measures the time during which the leader code is Low level     |

| REDATA:        | This area is used to store receive data                         |

| CODEBUF:       | Buffer area for last code input                                 |

| VALID:         | Test data for code validity check                               |

| FLAGS:         |                                                                 |

| VALFG (4EH.0): | Flag is set when a valid code is input                          |

| CPFG (4EH.1):  | Flag is set when a valid constant pulse is input                |

| FIRFG (4EH.2): | Flag is set when the first 60-ms pulse is input                 |

# **Programming Guidelines**

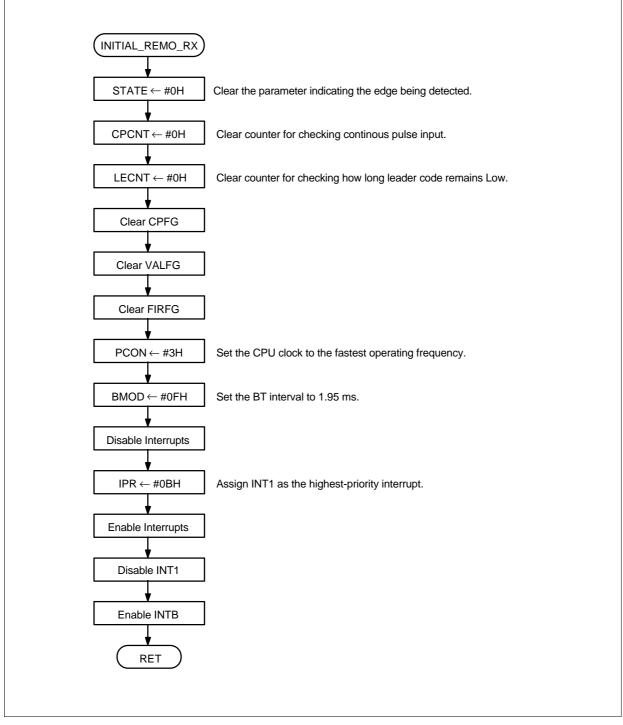

To properly initialize the basic timer, write the following values to the basic timer mode register and the IPR register:

| $BMOD \gets \#0FH$ | ; Select the basic timer interrupt with a 1.95-ms interval |

|--------------------|------------------------------------------------------------|

| $IPR \gets \#0BH$  | ; Select INT1 as the highest-priority interrupt            |

| Interrupts:        | INT1 and INTB                                              |

| I                  |                                                            |

| Nesting:           | Two levels                                                 |

| Port assignment:   | P1.1 (shared with INT1)                                    |

|                    |                                                            |

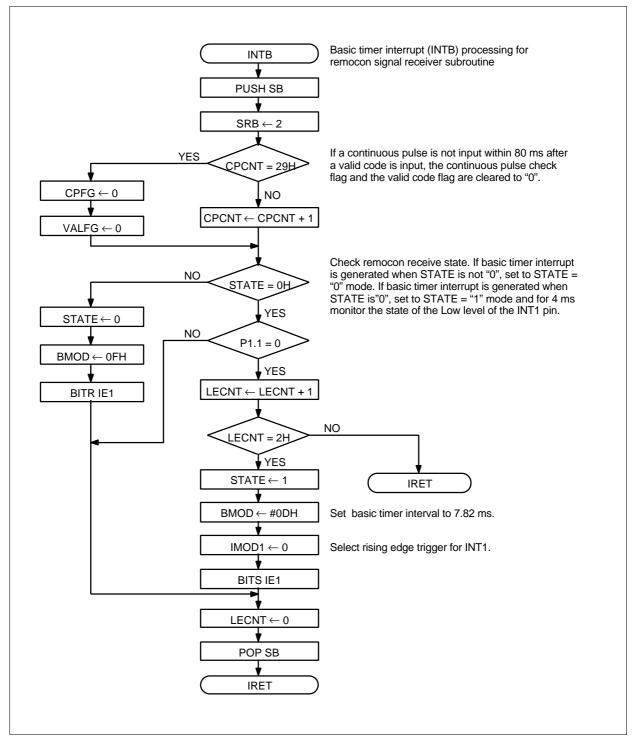

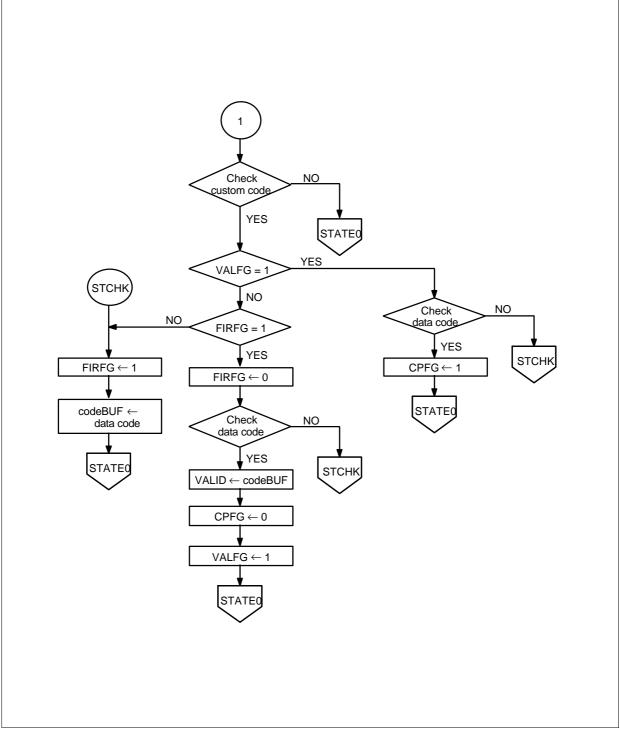

Figure 1-5. Program Flowchart for Basic Timer Interrupt (INTB) Processing

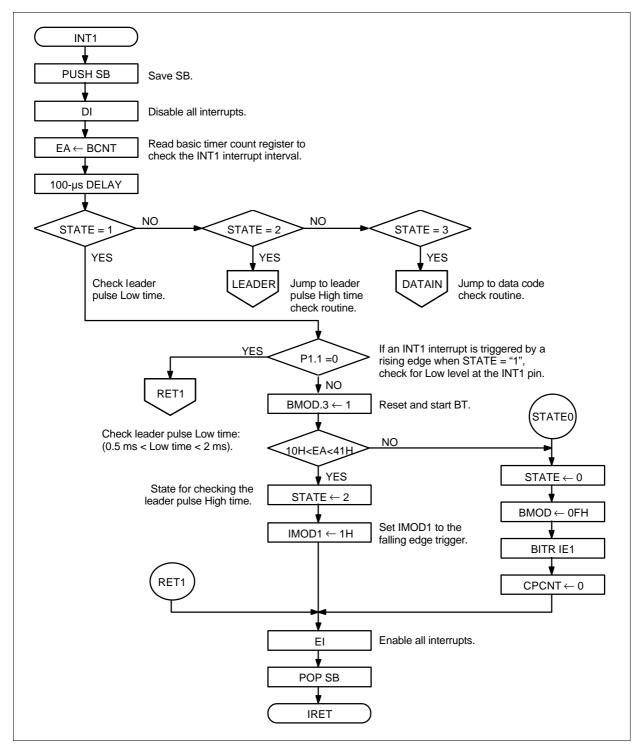

Figure 1-6. Program Flowchart for INT1 Processing

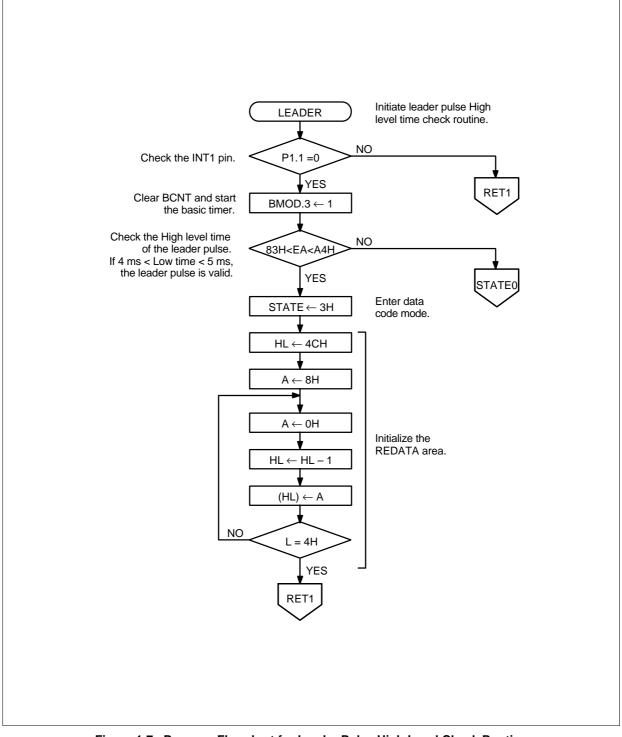

Figure 1-7. Program Flowchart for Leader Pulse High Level Check Routine

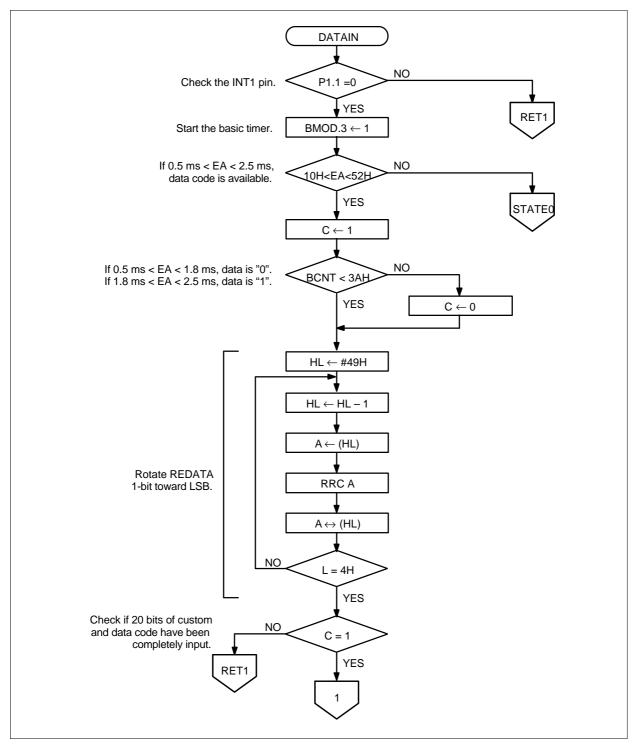

Figure 1-8. Program Flowchart for Data Code Check Routine

| ; CHIP                                                                                             | C:\SMDS                      | I\DATA\                   | 57C2408.DEF                                       |

|----------------------------------------------------------------------------------------------------|------------------------------|---------------------------|---------------------------------------------------|

| CPCNT<br>STATE<br>LECNT<br>REDATA<br>VALID<br>FLAG<br>VALFG<br>CPFG<br>FIRFG<br>CUSTOMA<br>CUSTOMB | ORG<br>VENT1<br>ORG<br>VENT3 | EQU<br>EQU<br>EQU<br>0000 | FLAG.1<br>FLAG.2<br>55H<br>56H<br>0H<br>NTB<br>6H |

; Initialize remocon receive subroutine:

| INITIAL_REMO_RX<br>BITR<br>LD<br>LD<br>LD<br>BITR<br>BITR<br>BITR<br>LD | EMB<br>EA,#00H<br>STATE,A<br>CPCNT,EA<br>LECNT,A<br>CPFG<br>VALFG<br>FIRFG<br>A,#3H |                                                |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------|

| LD<br>LD                                                                | PCON,A<br>A,#0FH                                                                    | ; Set to high-speed mode                       |

| LD<br>DI                                                                | BMOD,A                                                                              | ; Set timer interval to 1.95 ms                |

| LD                                                                      | A,#0BH                                                                              |                                                |

| LD<br>El                                                                | IPR,A                                                                               | ; Assign INT1 highest interrupt priority level |

| BITR<br>BITS<br>RET                                                     | IE1<br>IEB                                                                          |                                                |

; INTB processing:

INTB

| INTB          | PUSH<br>SRB<br>LD<br>LD<br>ADS<br>JPS                                                                                                        | SB<br>2<br>EA,CPCNT<br>YZ,#0D7H<br>EA,YZ<br>INCRIT                                                                                       | -<br>-<br>-<br>,                        | EMB = 0, SRB = 2<br>CPCNT = 29H check<br>Repeat code check in 80-ms intervals                                                                                                                                  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| · Present rei | LD<br>LD<br>BITR<br>BITR<br>mocon input t                                                                                                    | EA,#00H<br>VALID,EA<br>CPFG<br>VALFG<br>ime.check                                                                                        | •<br>•<br>•                             | Repeat input flag $\leftarrow$ "0"<br>Valid code input flag $\leftarrow$ "0"                                                                                                                                   |

| MODCHK        |                                                                                                                                              |                                                                                                                                          |                                         |                                                                                                                                                                                                                |

| MODERK        | LD<br>CPSE<br>JPS<br>BTSF<br>JPS<br>LD<br>INCS<br>NOP<br>CPSE<br>JPS<br>LD<br>LD<br>LD<br>LD<br>LD<br>LD<br>LD<br>LD<br>LD<br>LD<br>LD<br>LD | A,STATE<br>A,#0H<br>DISINT<br>P1.1<br>BTCLR<br>HL,#LECNT<br>@HL<br>BF<br>A,#1H<br>STATE,A<br>A,#0H<br>IMOD1,A<br>A,#0DH<br>BMOD,A<br>IE1 | • • • • • • • • • • • • • • • • • • • • | Not a valid state for leader pulse check<br>Check the INT1 pin<br>Increment LECNT<br>Check in 4-ms intervals<br>STATE $\leftarrow$ 1H<br>Select INT1 rising edge trigger<br>Set basic interval time to 7.82 ms |

| BTCLR         | LD                                                                                                                                           | A,#0H                                                                                                                                    |                                         |                                                                                                                                                                                                                |

|               | LD<br>LD<br>JPS                                                                                                                              | LECNT,A<br>IBF                                                                                                                           | ;                                       | $LECNT \gets OH$                                                                                                                                                                                               |

| DISINT        | BITR<br>LD<br>LD<br>LD<br>LD<br>JR                                                                                                           | IE0<br>A,#0H<br>STATE,A<br>A,#0FH<br>BMOD,A<br>BTCLR                                                                                     | -<br>,<br>,                             | STATE $\leftarrow$ 0H<br>Set basic interval time to 1.95 ms                                                                                                                                                    |

| INCRIT         |                                            |                                                      |   |                                                                                                                                                      |

|----------------|--------------------------------------------|------------------------------------------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | LD<br>ADS<br>LD<br>JPS                     | EA,CPCNT<br>EA,#01H<br>CPCNT,EA<br>MODCHK            | ; | $CPCNT \leftarrow CPCNT + 1$                                                                                                                         |

| IBF            | POP<br>IRET                                | SB                                                   |   |                                                                                                                                                      |

|                | ORG                                        | 0300H                                                |   |                                                                                                                                                      |

|                | JPS<br>JPS<br>JPS                          | LEADCK<br>LEADER<br>DATAIN                           | ; | Jump to routine that checks Low time of leader pulse<br>Jump to routine that checks High time of leader pulse<br>Jump to the data code check routine |

| ; INT1 proce   | ssing:                                     |                                                      |   |                                                                                                                                                      |

| INT1           |                                            |                                                      |   |                                                                                                                                                      |

|                | DI<br>PUSH<br>PUSH<br>PUSH<br>PUSH<br>PUSH | EA<br>HL<br>WX<br>YZ<br>SB                           | ; | Push EA, HL, WX, YZ, and SB values onto stack                                                                                                        |

| ; 100-µs DEl   | LAY:                                       |                                                      |   |                                                                                                                                                      |

|                | LD                                         | EA,#15H                                              |   |                                                                                                                                                      |

| LOP            | DECS<br>JR                                 | EA<br>LOP                                            |   |                                                                                                                                                      |

| ; Multiple bra | anch processi                              | ing:                                                 |   |                                                                                                                                                      |

|                | LD<br>LD<br>ADS<br>NOP                     | A,STATE<br>E,#0H<br>EA,#0FFH                         |   |                                                                                                                                                      |

|                | LD<br>ADS                                  | WX,EA<br>WX,EA                                       | ; | WX $\leftarrow$ (STATE – 1) $\times$ 2                                                                                                               |

| ; Read BCN     |                                            | ,                                                    | , |                                                                                                                                                      |

| LOOP1          |                                            |                                                      |   |                                                                                                                                                      |

|                | LD<br>LD<br>CPSE<br>JR<br>JR               | EA,BCNT<br>YZ,EA<br>EA,BCNT<br>EA,YZ<br>LOOP1<br>@WX | ; | Multi-level branch                                                                                                                                   |

|                |                                            |                                                      |   |                                                                                                                                                      |

1-14

| LEADCK        |                |                            |          |                                                          |

|---------------|----------------|----------------------------|----------|----------------------------------------------------------|

|               | BTST<br>JPS    | P1.1<br>RET1               | ;        | Check the Low level time of the leader pulse             |

|               | BITS<br>ADS    | BMOD.3<br>EA,#0F0H         | ;        | Restart the basic timer<br>EA > #10H                     |

|               | JPS            | STATE0                     | ,        |                                                          |

|               | ADS            | EA,#0DEH                   | ;        | EA < #0100 – #0DE + #1F = #41H<br>(0.5 ms < BCNT < 2 ms) |

|               | JPS            | STATE1                     | ;        | Yes                                                      |

| STATE0        |                | A #011                     |          | 07.175                                                   |

|               | LD<br>LD<br>LD | A,#0H<br>STATE,A<br>A,#0FH | ;        | $STATE \leftarrow 0$                                     |

|               | LD<br>BITR     | BMOD,A<br>IE1              | ;        | Set basic timer interval to 1.95 ms                      |

|               | LD<br>LD       | EA,#0<br>CPCNT,EA          | ;        | Clear CPCNT                                              |

| RET1          |                |                            |          |                                                          |

|               | POP<br>POP     | SB<br>YZ                   |          |                                                          |

|               | POP<br>POP     | WX<br>HL                   |          |                                                          |

|               | POP<br>El      | EA                         |          |                                                          |

|               | IRET           |                            |          |                                                          |

| STATE1        |                |                            |          |                                                          |

|               | LD<br>LD       | A,#1H<br>IMOD1,A           | ;        | Select INT1 falling edge trigger                         |

|               | INCS<br>JPS    | STATE<br>RET1              | ;        | $STATE \leftarrow 2$                                     |

| ; Leader puls | se check routi | ne:                        |          |                                                          |

| LEADER        | DTOF           | 544                        |          |                                                          |

|               | BTSF<br>JPS    | P1.1<br>RET1               | ;        | Check INT1 pin Low level                                 |

|               | BITS<br>ADS    | BMOD.3<br>EA,#7EH          | ;        | Restart the basic timer<br>EA > 83H                      |

|               | JPS<br>ADS     | STÁTE0<br>EA,#9DH          |          | EA < #100 – #9D + 41 = 0A4H                              |

|               | JPS            | STATE3                     | ;        | Yes                                                      |

| 074750        | JPS            | STATE0                     |          |                                                          |

| STATE3        | INCS           | STATE                      | ;        | STATE $\leftarrow$ 3                                     |

|               | LD<br>LD       | HL,#49H<br>A,#8H           | •        | # (VALID – 1) address MSB = "1"                          |

| Sauraa Cad    |                | Controllor Application (   | ,<br>Ca: |                                                          |

Source Code for Remote Controller Application (Cont.) REMO1

|                         | LD<br>DECS<br>LD<br>CPSE<br>JR<br>JPS                 | A,#0H<br>HL<br>@HL,A<br>L,#4H<br>REMO1<br>RET1                             | ;                                             | Clear all other bits                                                                                   |  |  |  |

|-------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------|--|--|--|

| ; Data input subroutine |                                                       |                                                                            |                                               |                                                                                                        |  |  |  |

| DATAIN                  | BTSF<br>JPS<br>BITS<br>ADS<br>JPS<br>ADS<br>JR<br>JPS | P1.1<br>RET1<br>BMOD.3<br>EA,#0F0H<br>STATE0<br>EA,#0BEH<br>DAT0<br>STATE0 | · ,<br>· ,<br>· ,<br>· ,<br>· ,<br>· ,<br>· , | Check P1.1<br>Start the basic timer<br>EA > 10<br>EA < 100 - 0BE + 10 = 2<br>Yes, 0.5 ms < EA < 2.5 ms |  |  |  |

| DAT0                    | SCF<br>ADS<br>RCF<br>LD                               | EA,#18H<br>HL,#49H                                                         | · ,<br>· ,<br>· ,                             | EA > 0FF - 18 - 0BE - 0F0 = 3AH<br>0.5 ms < EA < 1.8 ms data = "0"<br>1.8 ms < EA < 2.5 ms data = "1"  |  |  |  |

| DATABR                  | DECS<br>LD<br>RRC<br>XCH<br>CPSE<br>JR<br>BTST<br>JPS | HL<br>A,@HL<br>A,@HL<br>L,#4H<br>DATABR<br>C<br>RET1                       | - ,<br>,<br>,<br>,                            | Rotate remocon receive data one bit toward LSB<br>Check for 20-bit data input completion<br>No         |  |  |  |

; Custom code check routine:

|           | LD<br>LD<br>CPSE<br>JPS<br>LD<br>LD<br>CPSE<br>JPS<br>BTST<br>JR<br>LD<br>LD<br>CPSE<br>JPS<br>BITS<br>JPS | EA,REDATA<br>HL,#CUSTOMA<br>EA,HL<br>STATE0<br>A,REDATA + 2<br>E,#CUSTOMB<br>A,E<br>STATE0<br>VALFG<br>FIRCHK<br>HL,#(REDATA+3)<br>EA,VALID<br>EA,@HL<br>STCHK<br>CPFG<br>STATE0 | ; | Yes, 20-bit data input complete<br>Custom code = read custom data?<br>Check VALFG<br>Read data code = valid data code<br>Repeat key is pressed |

|-----------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------|

| FIRCHK    |                                                                                                            |                                                                                                                                                                                  |   |                                                                                                                                                |

|           | BTST<br>JPS<br>BITR                                                                                        | FIRFG<br>STCHK<br>FIRFG                                                                                                                                                          | ; | Check FIRFG                                                                                                                                    |

|           | LD<br>LD<br>CPSE<br>JPS                                                                                    | HL,#(REDATA+3)<br>EA,codeBUF<br>EA,@HL<br>STCHK                                                                                                                                  | ; | Read data code = codeBUF data                                                                                                                  |

|           | LD<br>LD<br>BITR<br>BITS<br>JPS                                                                            | EA,codeBUF<br>VALID,EA<br>CPFG<br>VALFG<br>STATE0                                                                                                                                | ; | $VALID \gets codeBUF$                                                                                                                          |

| STCHK     |                                                                                                            |                                                                                                                                                                                  |   |                                                                                                                                                |

|           | BITS<br>LD<br>LD<br>JPS                                                                                    | FIRFG<br>EA,REDATA+3<br>codeBUF,EA<br>STATE0                                                                                                                                     | ; | $codeBUF \leftarrow read data code$                                                                                                            |

| ; ======= |                                                                                                            |                                                                                                                                                                                  |   |                                                                                                                                                |

#### USING THE BASIC TIMER TO MEASURE PULSE WIDTH

#### **Function Description**

The following routine uses the basic timer to measure the width of the High-level pulse that is input at the INT4 interrupt pin (with both rising and falling edge detection). In this case, the pulse width does not exceed the basic timer counter (BCNT) value, which is at least 7.8 ms.

#### Source Code for Pulse Width Measurement Routine

|              | BUFF<br>BUFF                                               | EQU<br>EQU                                                                    | 30H<br>32.OH                                                                                                                                |

|--------------|------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| ; INT4 proce | essing:                                                    |                                                                               |                                                                                                                                             |

| LOOP         | LD<br>LD<br>CPSE<br>JR<br>BTST<br>JR<br>LD<br>BITR<br>IRET | EA,BCNT<br>YZ,EA<br>EA,BCNT<br>EA,YZ<br>LOOP<br>P1.3<br>AA<br>BUFF,EA<br>FLAG | <ul> <li>; EMB = "0"</li> <li>; P1.3 = "1"?</li> <li>; No</li> <li>; Store the BCNT value</li> <li>; Clear the data present flag</li> </ul> |

| AA           | LD<br>SBS<br>NOP<br>LD<br>LD<br>BITS<br>IRET               | EA,BUFF<br>YZ,EA<br>EA,YZ<br>BUFF,EA<br>FLAG                                  | ; Store data<br>; Set the data present flag                                                                                                 |